# Power Dissipation of NAND Gate based CMOSMultiplexer using Sleepy Keeper Technique

Er. PriyaVerma<sup>1</sup>

E-mail:<u>priyarajput22dec@gmail.com</u> <sup>1</sup>Department of Electronics & Communication Engineering, Sri Satya Sai University of Technology and Medical Sciences,Sehore(M.P.) **Dr. MukeshTiwari**<sup>2</sup>

E-mail:mukeshtiwari79@yahoo.co.in

<sup>2</sup>Professor, School of Engineering Sri Satya Sai University of Technology & Medical Sciences, Sehore (M.P)

**Abstract:** - As a consequence of the Moore's law, every year channel length of the MOSFET is reducing, causing Short Channel Effect (SCE). SCE is effecting the performance of the circuit designed using the low dimensional MOSFETs. High frequency performance and power consumption of the circuits is largely affected due to SCE. In today's world of consumer electronics there is a requirement of high frequency circuits which is having low power consumption so that it can be used in designing battery driven handheld devices. On the other hand there is a huge requirement of CMOS technology compatible device which can be used as poweramplifiers for communication devices like repeaters and routers. NAND gates is implemented using various technique approaches for digital schematic design such as sleepy keeper, stack approach, sleepy keeper etc. Power utilization analysis of the various method techniques for NAND gates is implemented. To implement and power utilization is analysis for NAND gates using sleepy keeper approach and comparing with various existing methods. It is also implement CMOS multiplexer using NAND gate and optimize power dissipation. The CMOS circuits is implementing DSCH and draw the layout of MICROWIND software.

Keywords: CMOS, NAND Gate, Sleepy Keeper, DSCH, MICROWIND

#### I. INTRODUCTION

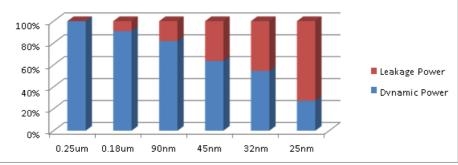

Reducing power dissipation has now become a critical design concern in almost all electronic systems. Reduction in the supply voltage is the most significant method for reducing the power dissipation because of thequadratic relationship between the supply voltage and the dynamic power dissipation [1]. To compensate for theperformance loss due to a lower supply voltage, threshold voltage of MOS transistors is also reduced. However, this causes an increase in the leakage current. Among all leakage currents, sub threshold leakage current is the most dominant [2]. This leakage current will become a large component in the total power dissipation is to develop effective circuit techniques to reduce this leakage current that is mainly caused by the reduction in the threshold voltage of MOS transistors and down scaling in technology (Roy et al. 2003). Technology scaling has allowed more functions per unit area, and lower dynamic power dissipation, but has alsoincreased the leakage power dissipation exponentially. An analysis of trends based on the International Technology Roadmap for Semiconductors (ITRS) shows that the leakage power dissipation is beginning to exceed the dynamic power dissipation with the down scaling in technology generation, which is shown in Fig.

1.1. In the past, circuit design techniques and architectures ignored the effects of leakage power dissipation because it was insignificant in comparison with the dynamic power dissipation. However, in modern technologies, the role of sub threshold leakage power dissipation cannot be ignored and now it has become dominant in the overall power dissipation in deep submicron and Nano-scale technologies [3, 4].

Figure 1: Leakage versus dynamic power dissipation trends with technology scaling

Although total power dissipation (dynamic and leakage) during the active mode is reduced with the scaling in the supply voltage, further power dissipation can only be reduced if standby leakage power dissipation is controlled wherever possible, since this leakage power will make up a larger percentage in the overall power dissipation with further scaling down in technology [5].

# **II. POWER DISSIPATION IN CMOS**

The power dissipation of CMOS circuits are usually comprised of three components namely Static power dissipation (SPD), Dynamic power dissipation (DPD) and Short circuit power dissipation (ScPD). The total power dissipation is represented by

### Total power dissipation = SPD + DPD + ScPD (1)

Reverse biasing, the diffusion area, and the CMOS transistor's surface are all major contributors to the static power loss. In most cases, leakage current and voltage supply are used to define SPD. However, the capacitance's charging and discharging creates the dynamic power dissipation. Dropping the load capacitor or rail voltage (Vdd) can make it intense. The navigation path that runs in the middle of the rail voltage (Vdd) and ground results in power loss during a short circuit. Power indulgence is primarily disrupted by sub-threshold leakage, gate-oxide excavation, and reverse bias intersection as a result of technological advancement. By disrupting the minimum voltage, increasing gate oxide thickness increases sub-threshold current and intensifies gate oxide tunneling current [6, 7].

The primary sources of power loss are:

1) The loss of capacitive power as a result of the load capacitance's charging and discharging;

2) Short circuit currents because there is a conducting path between the voltage supply and ground during a logic gate's brief transition; and

3) Current leakage. Sub-threshold and reverse-bias diode currents make up the leakage current.

The first is the result of stored charge between the active transistor drain and bulk, and the second is the result of carrier diffusion between the OFF transistor source and drain. By designing the circuit to have equal input and output rise/fall edge times, the short-circuit power dissipation can be reduced to 10% of the total power dissipation. Technology processes with feature sizes greater than 1 m are dominated by power dissipation from switching activity. As technology processes progress toward the deep-submicron regime, transistor feature sizes are shrinking, lowering load capacitances. The supply voltage must also be reduced as a result of the smaller feature size. For dynamic power savings, the voltage scaling method makes use of the quadratic dependence of switching power on supply voltage. However, this method incurs a cost for the operation of the circuit by significantly increasing the delay as the supply voltage approaches the devices' threshold voltage [8, 9].

# III. PROPOSED METHODOLOGY

This section explains the structure of the sleepy keeper approaches well as how it operates. In addition, we discuss some layout issues for the sleepy keeper approach. The basic problem with traditional CMOS is that the transistors are employed in their effective manner. PMOS transistor is applied with VDD supply and NMOS transistor is grounded.

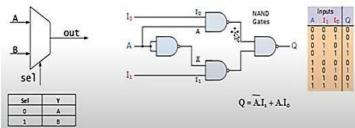

Figure 2: 2:1 MUX using NAND Gate

However the PMOS transistors are not effective while dispatching GND. Similarly the NMOS transistors arenot effective at passing VDD. In order to uphold the level "1" during sleep state, the sleepy keeper technique utilizes the output value of "1". An NMOS transistor is connected to VDD so that the output value is maintained to "1" during sleep state. A supplementary single NMOS transistor connected across the pull-up sleep transistor passes VDD to pull up network.

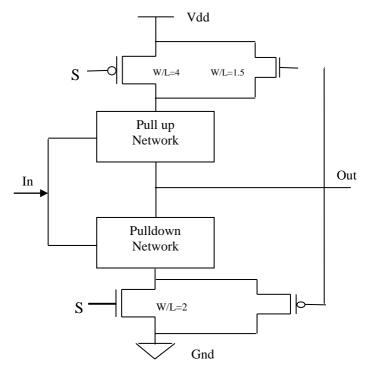

During sleep state, this NMOS transistor is the only source of VDD as the sleep transistor is kept off. As shown in Figure 3, an additional single NMOS transistor placed in parallel to the pull-up sleep transistor connects VDD to the pull-up network. When in sleep mode, this NMOS transistor is the only source of VDD to the pull-up network since the sleep transistor is off. As shown in figure 3.8, a supplementary single PMOS transistor is placed across the pull-down network. During sleep state, this NMOS transistor is the only source of VDD as the sleep transistor is kept off. It is the dual case of the output "1"case explained above. For this approach to work, all that is needed is for the NMOS connected to VDD and the PMOS connected to GND to be able to maintain proper logic state. This seems likely to be possible as other researchers have described ways to use far lower VDD values to maintain logic state. For example propose some significantly reduced VDD values sufficient to maintain state. We emphatically do not use sleepy keeper transistors (the NMOS connected to VDD and the PMOS connected to GND) to dynamically change the output voltage but instead only use them to maintain an already calculated output voltage. Specifically, only a few clock cycles after entering sleep to a few clock cyclesprior to leaving sleep do the sleepy keeper transistors acts as the sole connection to keep the output voltage unchanged.

Figure 3: Sleepy keeper approach

# **IV. SIMULATION RESULTS**

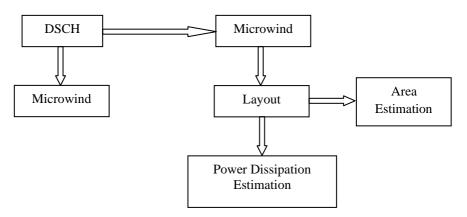

The proposed methodology is a sleepy keeper approach to reduce for power consumption. Here, the powerconsumption is observed by employing the DSCH and MICROWIND tool.

Figure 4: Block diagram

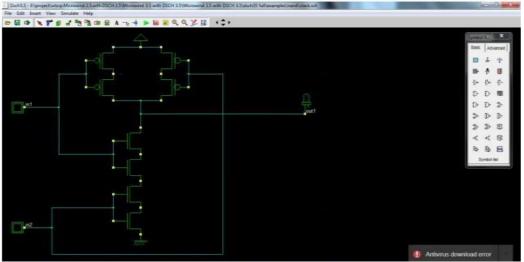

Designing Circuits the Figure 5 inferences the digital schematic diagram for basic NAND gate using microwindtool.

The Figure 6 inferences the digital schematic diagram for Zigzag approach NAND gate using microwind tool.

Figure 6: NAND gate using zigzag approach

The Figure 7 inferences the digital schematic diagram for dual stack approach NAND gate using microwindtool.

Figure 7: NAND gate using dual stack approach

The Figure 8 inferences the digital schematic diagram for sleepy keeper approach NAND gate using microwind tool.

Figure 8: NAND using sleepy keeper approach

The power utilized by basic NAND gate is 14.016( $\mu$ W). The power utilized by NAND using zigzag approach and dual stack is 2.328( $\mu$ W) and 1.033( $\mu$ W) respectively. The power utilized by NAND using stack and sleepy stack is 1.183 ( $\mu$ W) and 0.656 ( $\mu$ W) respectively. The power utilized by NAND using proposed sleepy keeper is0.595( $\mu$ W). The power utilized by basic NOR gate is 1.437( $\mu$ W). The power utilized by NOR using zigzag approach and dual stack is 1.347( $\mu$ W) and 1.850( $\mu$ W) respectively. The power utilized by NOR using stack and sleepy stack is 1.397( $\mu$ W) and 0.706( $\mu$ W) respectively. The power utilized by NOR using sleepy keeper is 0.644( $\mu$ W). The Figure 9 inferences the power utilized by dual stack approach NAND gate using microwind tool.

Figure 9: Power utilized by dual stack approach NAND gate

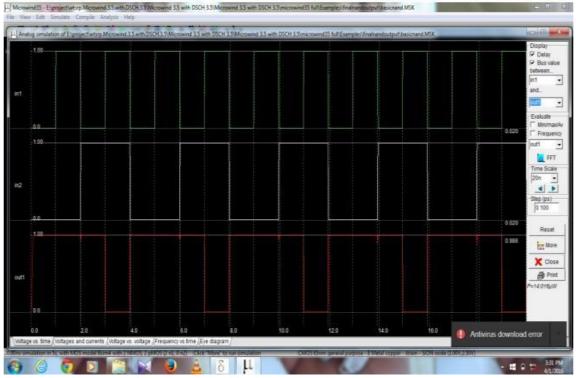

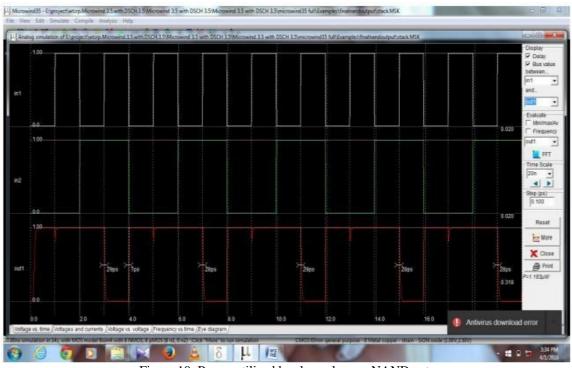

The Figure 10 inferences the power utilized by sleepy keeper approach NAND gate using microwind tool.

Figure 10: Power utilized by sleepy keeper NAND gate

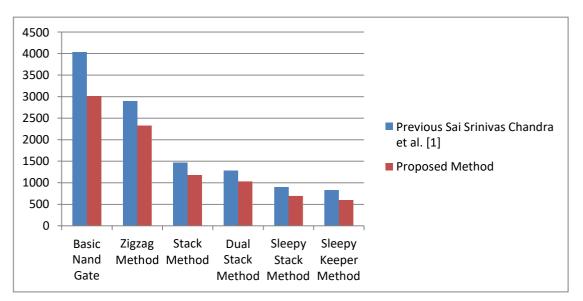

Table 1 represents the NAND gate using different methods. The basic NAND gate provide a power of 3016 nW,Zigzag method provide a power 2328 nW, Stack method provide a power 1183 nW, Dual Stack method provide a power 1033 nW, Sleepy Stack method provide a power 696 nW and Sleepy Keeper method provide a power 595 nW. Fig. 5.22 shows the graphical representation of the comparison method.

| Method               | Power (nW)            |                 |

|----------------------|-----------------------|-----------------|

|                      | Previous Sai Srinivas | Proposed Method |

|                      | Chandra et al. [1]    |                 |

| Basic Nand Gate      | 4036 nW               | 3016 nW         |

| Zigzag Method        | 2893 nW               | 2328 nW         |

| Stack Method         | 1467 nW               | 1183 nW         |

| Dual Stack Method    | 1282 nW               | 1033 nW         |

| Sleepy Stack Method  | 899.3 nW              | 696 nW          |

| Sleepy Keeper Method | 829.7 nW              | 595 nW          |

Table 1: Comparison of power utilization of NAND gate using various methods

Figure 11: Graphical Represent of NAND Gate

#### V. CONCLUSION

This method includes producing a numerous primary inputs, appraising the leakage of each input, and possession track of the best vector providing the minimal leakage current. A more well-organized way is to employ the genetic algorithm to exploit historical data to speculate on new search points with expected improved performance to find a near-optimal solution. The reduction of standby leakage power by application of an input vector is a very operational method of monitoring the sub threshold outflow in the standby mode of operation of a circuit. In a stack transistor insertion technique is given. For the gates with high sub threshold leakage in non-critical paths, a Leakage Control Transistor (low) is inserted in series and is turned off during thestandby mode. The technique can effectively diminish the leakage current by means of single-threshold voltage. We here review previously proposed circuit level approaches for sub threshold leakage power reduction. The most well-known traditional approach is the sleep approach.

# LIST OF ABBREVIATION

| S.No | Abbreviation | Definition                                          |  |

|------|--------------|-----------------------------------------------------|--|

| 1    | MOSFET       | Metal Oxide Semiconductor Field-Effect Transistor   |  |

| 2    | SCE          | Short Channel Effect                                |  |

| 3    | CMOS         | Complementary Metal Oxide Semiconductor             |  |

| 4    | NAND         | NOT AND                                             |  |

| 5    | DSCH         | Digital Schematic Circuit Designing software        |  |

| 6    | MOS          | Metal Oxide Semiconductor                           |  |

| 7    | ITRS         | International Technology Roadmap for Semiconductors |  |

| 8    | SPD          | Static power dissipation                            |  |

| 9    | DPD          | Dynamic power dissipation                           |  |

| 10   | ScPD         | Short circuit Power Dissipation                     |  |

| 11   | PMOS         | p-channel Metal Oxide Semiconductor                 |  |

| 12   | NMOS         | n-channel Metal Oxide Semiconductor                 |  |

# DECLARATIONS

#### 1. Funding Declaration

I, Priya Verma, first author of the research paper, hereby declare that I did not receive support from any organization for the submitted work. No funding was received to assist with the preparation of this.

#### 2. Data Availability Declaration

I, hereby declare that this research paper is a part of dissertation of my Ph.D. So complete data can be accessed after completion of it.

#### 3. Competing Interest Declaration

I, hereby declare that I have no competing interest that could appear to influence the work reported in this paper.

- 4. Consent to publish Declaration

- "Not Applicable"

#### 5. Author's Contribution

Study conception and design: Priya Verma; Data collection: Dr. Mukesh Tiwari; Analysis and interpretation of results: Dr.Mukesh Tiwari, Er. Priya Verma; Draft manuscript preparation: Er. Priya Verma. Both authors reviewed the results and approved the final version of the manuscript.

#### First Author: Priya Verma

#### ACKNOWLEDGEMENT

We would like to thank Dr. Lalit Mohan Choudhary, Assistant Professor, SSSUTMS, Schore for provding us with his guidance and support during our research.

#### REFERENCES

- [1] Sai Srinivas Chandra, R. Jagadeesh Kannan, B. Saravana Balaji, Sree hari Veeramachaneni & Sk. Noor Mahammad, "Efficient design and analysis of secure CMOS logic through logic encryption", ScientificReport (Scopus), Nature, 2023.

- [2] A. Gupta, M. K. Singh, R. Jaiswal, D. Goel and K. Singh, "Standard Cell Library Design of 2:1 Mux Using 45nm Technology", International Conference on Next Generation Electronics (NEleX), Vellore, India, pp. 1-5, 2023.

- [3] R. Singh and A. Kumar, "Design and analysis of a low power high speed full adder using 2×1 multiplexer," IEEE North Karnataka Subsection Flagship International Conference (NKCon), Vijaypur,India, pp. 1-7, 2022.

- [4] M. Sivasakthi and P. Radhika, "A High-Speed MCML Logic Gate and Multiplexer Design in 45 nm CMOS Technology," Fourth International Conference on Emerging Research in Electronics, Computer Science and Technology (ICERECT), Mandya, India, pp. 01-05, 2022.

- [5] K. Rajashekhar, Kiladibaboji and K. Mohana Leela, "Leakage Power, Current and Delay Analysis of Stack ONOFIC Based CMOS Circuits", International Conference on Advances in Computing, Communication and Applied Informatics (ACCAI), IEEE 2022.

- [6] D. R. Florance and B. Prabhakar, "Design of FinFET and GnrFET Based Full Adder Cell Using Multiplexer Selection Logic", 2022 4th International Conference on Smart Systems and Inventive Technology (ICSSIT), pp. 741-747, 2022.

- [7] H. You J. Yuan Z. Yu and S. Qiao "Low-Power Retentive True Single-Phase-Clocked Flip-Flop With Redundant-Precharge-Free Operation" IEEE Transactions on Very Large Scale Integration (VLSI) Systems vol. 29 no. 5 pp. 1022-1032 May 2021.

- [8] Ritesh Ray Chaudhuri William Simpson Michael Hurt and John Lee "Dashboard for CMOS (Complementary metal oxide semiconductor) Parametric Yield and Perf or. Monitoring in Semiconductor (SC) Manufacturing" 2021 32nd Annual SEMI Advanced S.C Manufacturing Conf. (ASMC) 2021.

- [9] Laxmi Kumre, Bhavana P Shrivastava and Neeraj Rai, "Comparative Analysis of CMOS Inverter For Low Leakage Power", International Journal Of Scientific & Technology Research Volume 8, Issue 09, September 2019.

- [10] Xiaoke Tang Xu Hu Yapeng Zhang Yi Hu and Xi Feng, "An Analysis of Power Dissipation Analysis and Power Dissipation optimization Methods in Digital Chip Layout Design", IEEE 19th Interna. Conf. on Comm. Tech. (ICCT) 2019.

- [11] S. Thayaparan and G.W.G.K.N. Udayanga "Minimum leakage vector with sparse power gating a combinational approach for standby leakage power reduction in CMOS (Complementary metal oxide semiconductor) circuits" 2019 IEEE Interna. Circ. and Sys. Sympo. (ICSyS) 2019.

- [12] R. Rao R. Katreepalli and E. R. Thuraka, "Design of general purpose microprocessor with an improved performance self-sleep circuit", International Conf. on Smart Sys and Inventive Tech. (ICSSIT) 2018.

- [13] S. Chaudhary and R. Lorenzo "Low leakage and minimum energy consum. in CMOS (Complementary metal oxide semiconductor) logic cir" Interna. Conf. on Electro. Design Comp. Netw.& Automated Verifi. (EDCAV) Jan. 2015.

- [14] A. Nunez and B. S. Deepaksubramanyan "Analysis of subthreshold leakage reduction in CMOS (Complementary metal oxide semiconductor) digital circ" Proc. 13th NASA VLSI Symp. June 2007.

- [15] Abdollahi, A, Fallah, F & Pedram, M., "Leakage current reduction in CMOS VLSI circuits by input vector control", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 12, no. 2, pp.140-154, 2004.

- [16] Anis, M, Mahmoud, M, Elmasry, M & Areibi, S, "Dynamic and leakage power reduction in MTCMOS circuits using an automated efficient gate clustering technique", in Proceedings of the 39th Annual Design Automation Conference, ACM, pp. 480-485, 2002.

- [17] Behradfar, A, Zeinolabedinzadeh, S & HajSadeghi, K, "A clock boosting scheme for low voltage circuits", 15th IEEE International Conference on Electronics, Circuits and Systems, pp. 21-24, 2008.

- [18] Brandt, J, Schneider, K, Ahuja, S & Shukla, SK, "The model checking view to clock Stating and operand isolation", Proceedings of the 10th International Conference on Application of Concurrency to System Design (ACSD), IEEE, pp. 181-1, 2010.

- [19] Keskin, M, "A low-voltage CMOS switch with a novel clock boosting scheme", IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 52, no. 4, pp. 185-188, 2005.

- [20] Kim, KK & Kim, YB, "A novel adaptive design methodology for minimum leakage power consideringPVT variations on nanoscale VLSI systems", IEEE Transactions on Very Large Scale Integration (VLSI) systems, vol. 17, no. 4, pp. 517-528, 2009.

- [21] Koppanalil, J, Yeung, G, Driscoll, DO, Householder, S & Hawkins, C, "A 1.6 GHz dual-core ARM Cortex A9 implementation on a low power high-K metal gate 32nm process", Proceedings of the International Symposium on VLSI Design, Automation and Test (VLSIDAT), IEEE, pp. 1-4, 2011.

- [22] Narendra, S, De, V, Antoniadis, D, Chandrakasan, A & Borkar, S, "Scaling of stack effect and its application for leakage reduction", in Proceedings of the International Symposium on Low Power Electronics and Design ACM, pp. 195-200, 2001.

- [23] Neau, C & Roy, K, "Optimal body bias selection for leakage improvement and process compensation over different technology generations", in Proceedings of the International Symposium on Low Power Electronics and Design ACM, pp. 116-121, 2003.

# Author's Biography

Er.PriyaVerma was born in Bhopal, India, in 1987.She received the Bachelor of Engineering Degree in Electronic and Communication Engineering from R.G.P.V. University, Bhopal in 2010 and her M. Tech degree from the same University in 2014 in VLSI Design and perusing her Ph.D. degree in Electronics & Communication Engineering from SSSUTMS, Sehore. She had been Faculty of engineering students in the college BIET, Jhansi two years and Bundelkhand University for two years. Her current research interest includes multiplexers, logic gates, VLSI design.she can be contacted at email id: priyarajput22dec@gmail.com.

Dr. Mukesh Tiwari is Professor at School of Engineering Sri Satya Sai University of Technology & Medical Sciences, Sehore (M.P). He received the Bachelor of Engineering Degree in Electronic and Communication Engineering in 2001 and his M. Tech degree in 2009 in Digital Communication & his Ph.D. degree in Electronics & Communication Engineering in 2018 from R.G.P.V. Bhopal. His Areas of Research Interest are Image Processing, Wireless Communication Systems and Secure Transmissions. He can be contacted at email id; mukeshtiwari79@yahoo.co.in